**ICEST 2009**

# Simplified SPICE Model of TOPSWICH

Dimitar Todorov<sup>1</sup>, Elissaveta Gadjeva<sup>2</sup> and Georgy Kunov<sup>3</sup>

Abstract – The paper is devoted on the development of simplified Spice model of TOPSwitch. The basic functional dependencies of the TOPSwitch control are considered. A simplified behavioral parameterized model of the functional description of its control is constructed. The computer PSpice macromodel is created in schematic view and in the form of text description of the subcircuit. The vaweforms representing the characteristics of TOPSwitch are given.

*Keywords* –Spice simulation, Model, Power Supply, SMPS, TOPSwitch

# I. INTRODUCTION

Modern development of electronics leads to continuous increasing the complexity of the electronic devices as a construction of relatively simple interconnected elements.

In practice, there exists a continuous process of consolidating the hardware nodes. This process of increasing the device complexity needs computer simulation and testing the non-faulty work by any conditions. This is expressed in the great extend in the design process of electronic units providing power supply to the electronic equipment. Complicated mathematical models are used to describe the functional behavior of complex networks, including modeling of non-electrical parameters. This model complication leads to a continuous need the increasing the computer speed and memory resources in the simulation process.

# II. PROBLEM FORMULATION

Typical examples of such models are the models of management units in SMPS (Switch Module Power Supply). Due to the high complexity, they are distributed in relatively simple structures of control chips.

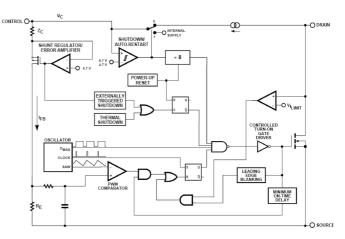

The processing of feedback information, the control of the pulse width modulation in starting, normal and critical modes of operation, are integrated in the more complex control structures such as TopSwitch. Typical examples are the elements of the series TopSwitch company Power Integrations [1] The simplified internal structure of TopSwitch is presented in Fig. 1.

Relatively complex in their structure *Spice* models are constructed in the contemporary description of the electrical

<sup>1</sup>Dimitar Todorov is with the Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Klimenrt Ohridski Blvd. 8, 1000 Sofia, Bulgaria, E-mail: <u>dgt@tu-sofia.bg</u>

<sup>2</sup>Elissaveta Gadjeva is with the Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Klimenrt Ohridski Blvd. 8, 1000 Sofia, Bulgaria, E-mail: egadjeva@tu-sofia.bg

<sup>3</sup>Georgi Kunov is with the Faculty of Electronic Engineering and Technologies, Technical University of Sofia, Klimenrt Ohridski Blvd. 8, 1000 Sofia, Bulgaria, E-mail: gkunov@tu-sofia.bg and nonelectrical processes. This is performed in order to assess entirely the specific features of the modeled process.

Simplified models of the electronic components are used in the analysis of complex circuits, including electrical and non-electrical parameters, in order to describe physical processes.

At the present there is no reported a model for the simulation of such devices [2]. The idea of the present paper is to create a relatively simple and sufficiently effective mathematical model using the basic principles of behavior modeling of power integrated circuit and relatively simple mathematical description and performance features.

# III. STRUCTURE OF TOPSWICH

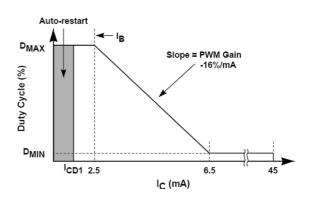

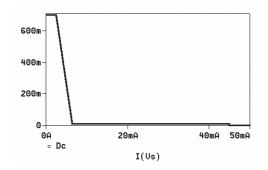

The basic idea of the control structure of TopSwich is that the control of the duty cycle of the width-pulse modulation of the chip is realized by monitoring of the current generated by the feedback displaced of the start and stop voltage levels as shown in Fig. 2.

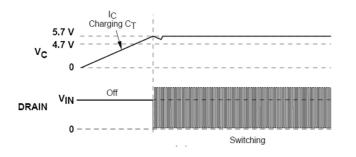

The dependence of the charge on the control element voltage during the startup process and normal operation is presented in Fig. 3.

Fig. 1. Simplified internal structure of TOPSwich

**ICEST 2009**

## Fig. 2. The dependence of the duty cycle on the monitoring current

Fig. 3. The dependence of the charge on the control element voltage during the startup process and normal operation

Fig. 5. Simplified functional structure of TOPSwich

It demonstrates the need of a minimal energy level of the feedback in connection with the process of standby and normal TOPSwitch operation.

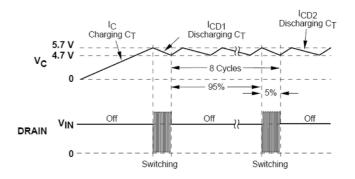

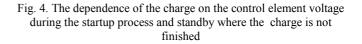

The dependence of the charge on the control element voltage during the startup process and the standby process (when the charge is not finished), is presented in Fig. 4.

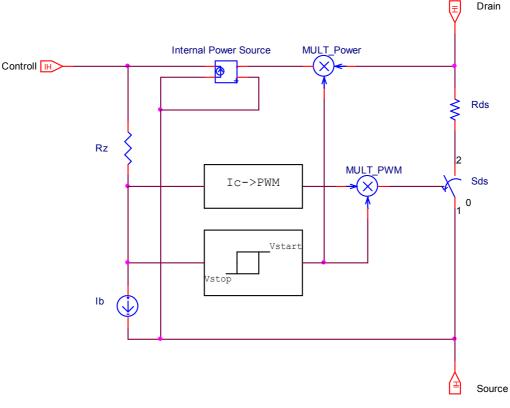

Based on the described above specific features in the TOPSwich operation, its functional structure is synthesized, as shown in Fig. 5.

A simplified *SPICE* model is constructed, corresponding to this structure. The basic functional dependencies of the

TOPSwitch control are considered. Computer realization of the parameterized model corresponding to the functional description of the TOPSwich control is developed.

The basic element in this structure is the functional converter Ic  $\rightarrow$  PWM. Due to its significant importance in the SMPS operation, the principle of its *SPICE* model description is considered in the present work.

The minimal energy levels of self-start and break of the work of TOPSwitch are presented with a logical function of the Schmitt trigger type.

$\label{eq:percentration} \\ \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \end{tabular} \\ \end{tabular} \end{ta$

Fig. 6. PSpice realization of the TOPSwitch model

## IV. DESCRIPTION OF THE PSPICE MODEL

The dependence of the duty cycle  $D_c(t)$  on the monitoring current  $I_c(t)$  has the form:

$$D_{c}(t) = \begin{cases} D_{\max} & \text{for } i_{c}(t) \leq I_{c1} \\ D_{\max} \frac{i_{c}(t) - I_{c2}}{I_{c1} - I_{c2}} & \text{for } I_{c1} < i_{c}(t) < I_{c2} \\ D_{\min} & \text{for } I_{c2} \leq i_{c}(t) < I_{c3} \\ 0 & \text{for } i_{c} \geq I_{c3} \end{cases}$$

(1)

The pulse width is:

## $PW(t)=PER.D_c(t)$

The *PSpice* realization of the model is presented in Fig. 6.

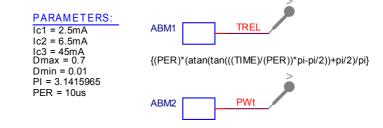

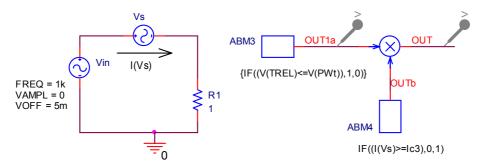

Using the block ABM of type **ABM** a signal V(TREL) is created of value, equal to the time interval TREL from the beginning of the current rectangle pulse. The function **mod(a,b)** is used for this purpose, which returns the remainder when **a** is divided by **b** [3]:

$$\operatorname{mod}(a,b) = \frac{b}{\pi} \left( \operatorname{arctan}\left( \tan\left(\frac{a}{b}\pi - \frac{\pi}{2}\right) \right) + \frac{\pi}{2} \right)$$

(2)

In the developed model:

$$TREL = mod(TIME, PER), \qquad (3)$$

where TIME is the current value of the time, and PER is the period of the pulse sequence.

The description of the expression (3) in the *PSpice* realization of the model (block *ABM*1) has the form:

The statement **IF-THEN-ELSE** is used for the modeling of pulses when the current  $I_c$ , which controls the duty cycle  $D_c$  according to (1), is less than  $I_{c3}$ :  $I_c < I_{c3}$ .

The pulse width is obtained as a signal value V(PWt) using the block *ABM*2 of type **ABM**:

In order to realize the condition:

$$D_c(t) = 0 \quad \text{sa} \quad i(t) \ge I_{c3} \quad ,$$

the block *ABM*4 of type **ABM** with a description of the output signal:

$$V_{OUTb} = \begin{cases} 1 \text{ for } i(t) < I_{c3} \\ 0 \text{ for } i(t) \ge I_{c3} \end{cases}$$

It is modeling using the IF-THEN-ELSE expression

V(OUTb) = IF(I(Vs)) >= Ic3, 0, 1)

In order to create rectangle pulses with a variable duty cycle  $D_c(t) = f(I_c)$ , the block *ABM*3 of type **ABM** with the following description is used:

$$V(OUTa) = \{ IF((V(TREL) \le V(PWt)), 1, 0) \}$$

**ICEST 2009**

Fig. 7. The dependence  $D_c = f(I_c)$

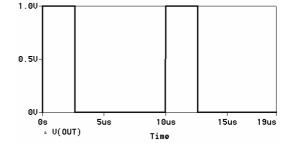

Fig. 8. The pulse sequence V(OUT) for  $I_c$ =5mA

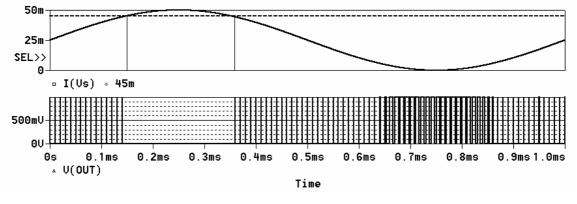

Fig. 9. The pulse sequence with variable duty cycle  $Dc(t) D_c(t) = f(I_c(t))$

The signals V(OUTa) and V(OUTb) are multiplied using the multiplier element MULT1 of type **MULT** from the **ABM** library. As a result, the pulse sequence V(OUT) is obtained.

The defined parameters using the pseudo-component **PARAMETERS** are included in the input *.cir* file in the form:

.PARAM Ic1=2.5mA, Ic2=6.5mA, + Ic3=45mA, Dmin=0.01, Dmax=0.7, + PER=10us

The dependence  $D_c = f(I_c)$  is shown in Fig. 7. The obtained pulse sequence V(OUT) is visualized in *Probe* as shown in Fig. 8 for Ic=5mA.

The pulse sequence with variable duty cycle  $D_c(t) = f(I_c(t))$  is presented in Fig. 9.

# V. CONCLUSION

A simplified and effective behavioral Spice model of TOPSwitch has been developed. The basic functional dependencies of the TOPSwitch control are considered. The computer parameterized\_*PSpice* macromodel is created in schematic view and in the form of text description of the subcircuit. The vaweforms representing the characteristics of TOPSwitch are given.

### ACKNOWLEDGEMENT

The investigations are supported by the R&D project 091ni041-03/2009 with the Technical University of Sofia.

#### REFERENCES

- [1] Power Integrations HandBook and Manual Design, NJ 2003

- [2] http://www.powerint.com/en/forum/power-supplydesign/top258

- [3] MicroSim Application Notes, appnts.pdf, 1997.

- [4] PSpice User's Guide, Cadence Design Systems, 2003.