# Subtraction Procedure for Drift Removing from ECG: High Level Synthesis with Compaan

## Tsvetan Shoshkov<sup>1</sup>

*Abstract* – The electrocardiogram (ECG) is often contaminated with drift interference. The subtraction procedure has proved its efficiency in removing the drift from the ECG.

Development process of such device is prone and time consuming. High level synthesis (HLS) solves these problems. In this paper HLS tools are used to develop a device for drift removing. FPGA is used as a target platform. Automatic output generation is used to make the reconfiguration and further development easier and faster.

Keywords – ECG, drift, FPGA, HLS, Compaan.

#### I. INTRODUCTION

Drift interference is often present in the Electrocardiogram (ECG) due to complex mechanical and electro-chemical electrode-to-skin processes. The subtraction procedure shows good results in removing baseline drift from ECG signals [2]. The subtraction procedure algorithm is modeled in Matlab. Based on these algorithms is developed a hardware design for drift removing form ECG [1]. This design realizes the subtraction procedure for real time operation. It is developed using VHDL and FPGA as a target platform. This standard manual development process using VHDL is error prone and time consuming. The design often must be reconfigured which is also a difficult process.

Fig. 1. Compaan Design Flow Basic Stages

In [5] are presented several system level development technologies. Automated high level system generation helps the development process and makes it easier and faster. In the present work we choose Compaan to develop a design for drift removing from ECG using the Subtraction Procedure. Compaan is a high level synthesis tool [4]. Compaan is used in the current work because it can provide full system integration. It can implement not only the hardware and software implementation but also the communication and integration between them.

Compaan design flow basic stages are shown on fig. 1. Compaan works with simple C code input specification. Khan Process Network (KPN) model of computation is used [4]. KPN specification is automatically generated based on the input. After that target platform and mapping specification are defined. Then software and hardware implementation can be automatically generated. Quick changes in the input specification are enough to automatically generate a new design and reconfigure the target platform.

## II. SUBTRACTION PROCEDURE FOR BASELINE DRIFT REMOVING

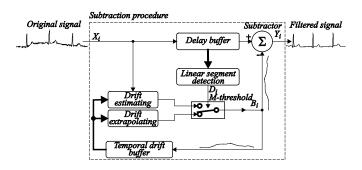

The process flow of the Subtraction Procedure is shown on fig. 2. Its structure contains three main stages:

- Linear segments detection. Each ECG sample is checked if it belongs to a linear segment by using appropriate linearity criterion. The linearity is defined by comparing the criterion with a predefined threshold M.

- Baseline drift calculation. If it is detected a linear segment the baseline drift is calculated using a digital filter and it is stored in a temporal FIFO buffer. In the same time the baseline drift is subtracted from the linear segment;

- Baseline drift extrapolation. If the current sample belongs to a nonlinear segment the value of the drift is calculated using the data stored in the temporal buffer and it is subtracted from the signal in a nonlinear segment.

Fig. 2. Basic Structure of the Subtraction Procedure for Baseline Drift Removing.

More details about the subtraction procedure for baseline drift removing are given in [2], [3]. The present work is focused on the implementation of the subtraction procedure for ECG drift removing in real time using Compaan design flow.

<sup>&</sup>lt;sup>1</sup>Tsvetan Shoshkov is with the Faculty of Electronics at Technical University of Sofia, 8 Kl. Ohridski Blvd, Sofia 1000, Bulgaria, E-mail: tsh@tu-sofia.bg.

#### **III. COMPAAN DESIGN FLOW**

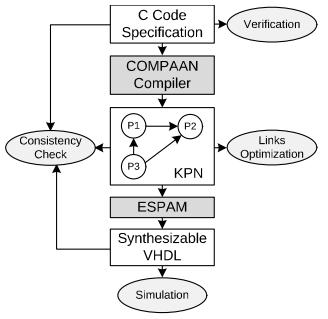

Compaan design flow is centered on Compaan compiler and ESPAM tools [4]. The application must be specified as parameterized static affine nested loop which is a subset of the C language. Fig. 3 presents a detailed block diagram of the used Compaan design flow.

Fig. 3. Compaan Design Flow.

Compaan compiler automatically generates a KPN model of computation based on the input C specification. Processes are further processed by Compaan to obtain hierarchical sub networks. Target platform is selected to generate a platform specification. Processes of the KPN specification are mapped on HW (FPGA) and mapping specification is automatically generated. HW is automatically generated by ESPAM based on the specifications generated in the first step. [3]

Nodes implemented with HW are using processors, which are composed of three separate blocks - read, execute and write. The read block waits until there are tokens ready to be read. A deep pipeline can be integrated in the execution block. When there are processed tokens ready to be sent the write block writes them into the corresponding communication link if there is space available. This structure provides the nodes with the ability to work independently of each other. Inside each node there is a constant track of the data, using iteration counters. Compaan tool allows simulation and verification of the system at each stage of development. It can optimize the size of the communication links based on the current application. [3]

Compaan design flow is producing low power consuming and fault tolerant designs. Fault tolerance is based on the simplicity and higher abstraction of the input specification. Constant track of the data inside each node also contributes to make the system more fault tolerant. The asynchronous work inside the design makes it low power consuming since each node is working only where there is data to be processed. Memory is main source of power consumption and communication links size optimization is also a very important feature.

The reconfiguration of the system using Compaan design flow is easy. It requires modification of the input C code and following the Compaan design flow to generate bit stream that can be used to reconfigure the hardware.

## IV. IMPLEMENTING THE SUBTRACTION PROCEDURE FOR DRIFT REMOVING WITH COMPAAN

The basic structure and elements of the Subtraction Procedure are shown on fig. 2. We use the Compaan design flow which is shown on fig 3 to implement the subtraction procedure for drift removing. All development flow steps are presented in this section. First input specification is created, after that KPN is automatically generated. Finally synthesizable VHDL code is automatically generated. More details for each step are listed in the following subsections.

#### A. Input Specification

As a first step of the development it is created the input SW specification. Short fraction of the C code input specification is present to picture its main concepts:

```

#pragma compaan_procedure ecg_drift

void filter(int data_in[WIDTH], int data_out[WIDTH],

int drift_out[WIDTH], int cr_out[WIDTH], int

cfr out[WIDTH])

int ecg[WIDTH];

cr[WIDTH];

cfr[WIDTH];

int ecq out linear[WIDTH];

int ecg_out_non_linear[WIDTH];

int ecg_drift[WIDTH];

int ecg_filtered[WIDTH];

int i, i, x;

ecg_drift[0] = 0;

// Stream data into the design

for (i = 1; i <= WIDTH; i = i + 1) {

ecg[i] = data_in[i];

}

// Data processing

for (j = 1; j <= WIDTH; j = j + 1) {</pre>

// Linearity criterions calculation

linearity_criterion(ecg[j], &cr[j], &cfr[j]);

// Baseline drift extrapolation

non_linear(ecg[j], ecg_drift[j-1],

&ecg_out_non_linear[j]);

// Baseline drift calculation

linear(ecg[j], ecg_drift[j-1], cfr[j],

&ecg_out_linear[j]);

// Switch between linear and non linear

cr_switch(cr[j], ecg_out_linear[j],

ecg_out_non_linear[j], &ecg_drift[j]);

// Subtract drift from the original signal

subtract(ecg[j], ecg_drift[j],

&ecg_filtered[j]);

}

```

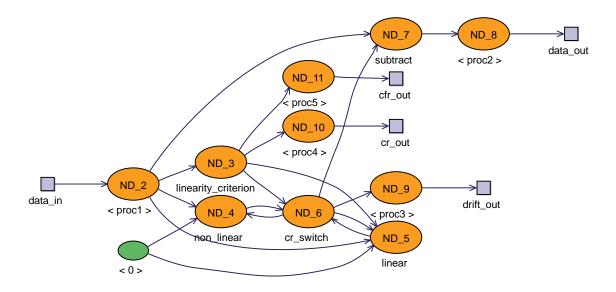

Fig. 4. Subtraction Procedure Baseline Drift Removing KPN.

```

// Stream data out

for (x = 1; x <= WIDTH; x = x + 1) {

data_out[x] = ecg_filtered[x];

drift_out[x] = ecg_drift[x];

cr_out[x] = cr[x];

cfr_out[x] = cfr[x];

}</pre>

```

Functions are called inside static affine nested loops to process the data. Inputs and outputs of the functions are given as parameters. Output parameters are specified as addresses to variables where the result is stored. Feedbacks from the output drift to the linear and non-linear segment calculations are realized.

First step in the specification is to stream in data into the design. After the actual processing starts with the first block witch is linearity criterion calculation. Functions for linear and nonlinear segment filtrations are present. Another function switches between the nonlinear and linear output based on the linearity criterion. The drift interference is subtracted by the original ECG signal. In the end the data is streamed out.

#### B. KPN Model of Computation

}

Compaan compiler is used to automatically generate KPN specification. This KPN specification can be used as a basis to generate the actual implementation of the device. It defines the dependencies between the nodes and connections between them.

The KPN is simulated to automatically optimize the communication link sizes. Fig. 4 shows the produced KPN for drift removing from ECG using the Subtraction Procedure. Each function from the input specification is realized using a separate processing node. Additional processing nodes are used to stream data in and out from the design.

#### C. Implementation

Next step of the Compaan design flow is selecting target platform and mapping creation. In our case we use default target and mappings, since we want to generate a project to simulate. After we have the KPN, platform and mapping specifications ready, we can generate synthesizable VHDL code. Each node is mapped to a hardware processing core. It consists of read, execute and write section. Each execution section must be additionally filled with the actual processing equations. The manually filled code realizes the relation between the inputs and the outputs in each block. Here is a fraction of the code realizing the linearity criterion calculation:

```

CR_CALC : process (CLK)

variable temp : std_logic_vector(31 downto

(0);

begin

if rising_edge(CLK) then

if (RST='1') then

temp := (others => '0');

else

temp := abs(XB(0) - (XB((25-1)/2)(30))

downto 0) & '0') + XB(25-1));

if (temp(temp'high) = '0') then

cr <= "00" & temp_sum(31 downto 2);</pre>

else

cr <= "11" & temp_sum(31 downto 2);</pre>

end if;

end if;

end if;

end process; -- CR_CALC

```

At each step of the development flow we perform consistency check with the other stages to define if there are any errors. Thus errors are easy to be identified and fixed at earlier stages of the development.

### V. EVALUATION AND RESULTS

Main target of our evaluation is to check if the generated design satisfies the application requirements. The development time is also a major aspect in this research. The system design must meet the functional and performance requirements and at the same time must be low power consuming and fault tolerant.

We use Xilinx ISE Design Suite 14.7 to simulate and verify the design. Virtex 6 FPGA is used as a target platform. ML605 evaluation kit with 200 MHz system clock is used. Compaan automatically generates a test bench that streams in and out data from the design. We use ECG signal provided by the American Health Association to test our design. Finally we use Matlab to plot the signals in graphics.

Fig. 5. Drift Removing Result Signals.

Fig. 5 shows two samples with input and output result signals obtained by the simulation of the design: The results obtained prove that the integrated design realizes the subtraction procedure for drift removing according to the modeled algorithms.

The design implementation of Compaan suggests that the processes inside are working asynchronously. The HW IP cores are working independently of each other, so they can work only when there is input data to be processed. This way it is achieved low power consumption. Another main point sufficient for low power consumption is the link sizes optimization that is automatically performed.

A manual VHDL implementation of the subtraction procedure for baseline drift removing is presented in [1]. In the current work we use Compaan design flow to develop the same drift removing processing algorithm. Table 1 presents a comparison between the development times consumed in the two cases. The comparison points that using Compaan the development time required is considerably decreased.

TABLE I Development time consumed

| Development Method      | Man-Months |

|-------------------------|------------|

| Manual VHDL Development | 0.75       |

| Compaan Design Flow     | 0.25       |

Automation of the generation and optimization benefit the development process. Using Compaan errors can be detected in earlier stages of the development.

#### **VI.** CONCLUSION

In this paper we present a high level synthesis of the subtraction procedure for drift removing from ECG. We use Compaan design flow to automatically generate an output design based on simple input specification. This considerably decreases the development time required. Compaan further optimizes the design and makes it fault tolerant and low power consuming.

The automatic generation of the output makes the development faster and easier. Slight changes in the input specification can be made and a new design can be easily regenerated. This benefits the research and development process. Quicker further investigations in this field can be achieved.

#### REFERENCES

- [1] Ts. Shoshkov, G. Mihov, "Subtraction Procedure for Removing the Baseline Drift from ECG Signals: Adaptation For Real Time Operation With Programmable Devices", ICEST 2013, Ohrid.

- [2] G. Mihov, I. Dotsinsky. "Subtraction Procedure For Removing The Baseline Drift From ECG Signals", Annual Journal of Electronics, pp. 118-122, 2010.

- [3] G. Mihov, I. Dotsinsky, C. Levkov, R. Ivanov, "Generalised Equations and Algorithm of the Subtraction Procedure for Removing Power-line Interference from ECG", Proceedings of the Technical University of Sofia, Vol. 58, b. 2, Sofia, pp. 31-38, 2008.

- [4] T. Stefanov, C. Zissulescu, A. Turjan, B. Kienhuis, Ed Deprettere. "System Design using Khan Process Networks: The Compaan/Laura Approach", DATE, Paris, 2004.

- [5] A. Gerstlauer, C. Haubelt, A. Pimentel, T. Stefanov, D. Gajski, J. Teich, "Electronic System-Level Synthesis Methodologies", IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 28, No. 10, pp. 1517-1530, 2009.