### Optimization and analysis ALL Digital PLL For resonant inverter

Goran Goranov<sup>1</sup>, Nikolay Madzharov<sup>2</sup>

**Abstract** – The purpose of this article is to determine the optimal ALL digital PLL for control resonant inverters. Various methods of synthesis of the digital frequency are examined and compared. On the base of the results we determine which control approach is applicable. Phase detector, loop filter and digital controlled oscillator realized in programmable logic are used.

Keywords – Logic gates, Control system, PLL, CPLD.

&iCEST 2016

### I. INTRODUCTION

The widespread use of transistor converters in various areas of practice - industry, medicine, service sector etc., imposes the new requirements to the control systems related with regulation and maintenance of certain operating modes. The implementation of the PLL functions into control systems for power converters and their investigation are presented in details in [1], [2], [3]. The use of programmable logic devices allows for the development of such systems by expanding their functionality and adaptability.

The optimization and analysis on this digital PLL gives us opportunities to work in a relatively wide frequency range and small steps for adjustment. This is also and an easy connection to other digital systems. The digitally frequency synthesis is based on programmable divide a quartz stabilized frequency to obtain a change of the output frequency in a certain range and a predetermined step. There are various methods for digital frequency synthesis - a divisor of N, direct digital synthesis (DDS), I/D - counter, fractional N, division by comparison schemes, etc. They are hardly realizable in a discrete implementation [4], [5], [6].

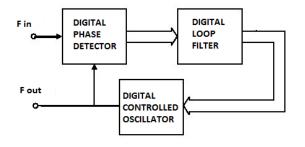

The analysis of digital PLL is limited to the examination of each module separately - Fig.1.

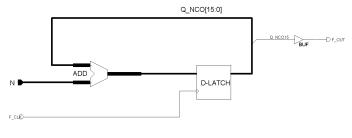

In the previous studies and researches of the author feasibility of a digital PLL, using I/D - counter and FRACTIONAL N method are affected. The conclusion is that various digital controlled generators require a substantial change in the functions of the previous blocks in the digital PLL. Often this refers to the digital filter, which is connected to the generator. Phase detector in most of the cases does not change unless you change monitoring requirements for the phase difference. Figure 1 shows a digital PLL, comprising a

<sup>1</sup> Assist. Prof. Goran Goranov, Ph. D., at Department "Electronics" of Technical University of Gabrovo, 5300 Gabrovo, 4 Hadji Dimitar st., Bulgaria, e-mail: <u>g\_goranov@bitex.bg</u>.

<sup>2</sup> Assoc. Prof. Nikolay Madzharov, Ph.D., at Department "Electronics" of Technical University of Gabrovo, 5300 Gabrovo, 4 Hadji Dimitar st., Bulgaria, e-mail: <u>madjarov@tugab.bg</u>. phase detector DPD, converting the phase difference into a signal of a specified duration, the digital filter DLF, converting the signal from the phase detector and the digital controlled oscillator DCO. In operation of the system, frequency *Fout* of the output signal of the DCO seeks to achieve input frequency *Fin* with certain accuracy. The change of the input frequency *Fin* generates an increase or decrease of the phase difference between it and the output frequency *Fout*, which leads to their alignment (*Fin = Fout*).

Fig. 1. ALL digital PLL

#### II. SYNTHESIS OF THE BASIC MODULES

### Phase detector.

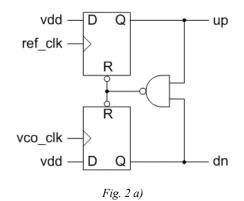

The most felicitous for use from the three main types of phase detectors (XOR, JK-Flip Flop and frequency phase detector) in the management scheme of the resonance inverters is the frequency phase detector. This is a detector with three states, managed by the front of the input signal. The range is  $\pm 360^{\circ}$ . From the timing diagram shown in Figure 2 we can see the advantage of the phase frequency detector. In phase difference  $\phi = 0$  signals UP and DN are also zero. Depends on the direction of the phase shift, in one of the two outputs, is obtained the pulse K<sub>3</sub>, proportional to the phase difference.

# <u>åicest 2016</u>

### Digital controlled oscillator

### FRACTIONAL - N

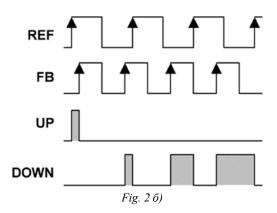

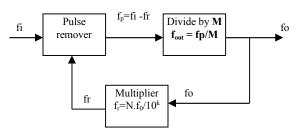

The block diagram representing the method consists of two main blocks for division of an integer and a fractional part - Fig. 3

Fig.3. Basic Fractional-N.

The input clock frequency  $f_i$  is used. Part of the pulses is removed in reducing impulses block. The number of the removed pulses is proportional to the ratio N, issued by the block of the multiplier. The removal of the phase noise (asymmetry between successive pulses) is achieved most easily as "blur" in time. The division factor M is used, which is an integer - block divider of M. The output frequency is calculated by the following formula:

$$f_{out} = \frac{f_p}{M} = \frac{f_i - f_r}{M} = \frac{f_i - \frac{N \cdot f_{out}}{10^k}}{M} , \qquad (1)$$

from where

$$f_{out} = \frac{f_i}{M + \frac{N}{10^k}},\tag{2}$$

$$f_{out} = \frac{f_i}{M + \frac{N}{10^k}} - \frac{f_i}{M + \frac{N-1}{10^k}},$$

(3)

In the presented formulas M is an integer, K is number of decades, and N is an integer in the range of 0 to  $10^{\kappa} - 1$ . On this basis, for the realization of FRACTIONAL - N method are needed binary decimal counters for M divider and multiplier for divisor N. If the coefficient of division M varied from 0 to 9, you will need a counter with two digits of M i.e. an amendment from 0 to 99, respectively, two counters and etc. The same goes and for the divisor N, which determines the fractional part. For example in the number of decade K=2 is obtained by dividing the frequency 1,00 to 99,99.

The implementation of the digital Fractional-N divider for management of the resonant inverter has the following advantages and disadvantages:

- ➢ Works in a wide frequency range.

- Receives relatively low phase noise and hence little impact on the optimal operation of the power transistor converters.

- Easy to implement coordinating digital filter

### Disadvantages:

- Nonlinear step of modifying the frequency depending on the divisor.

- Receives relatively low phase noise and hence little impact on the optimal operation of the power transistor converters.

### DDS – generator

DDS – generator is a type of generators, which is driven by a digital code (word), called the DCO. It works with digital converter filter time-digit code. On Fig. 4 is shown the block structure of this type of frequency synthesis.

The output frequency is given by:

$$f_{out} = f_{clk} \cdot N/2^k \tag{4}$$

where  $2^k$  is the sparsity of the ADD.

The amendment of  $f_{\text{out}}$  varies from 0 [Hz] to  $f_{\text{clk}}/2$  [Hz] with step:

$$\Delta f_{\text{out}} = f_{\text{clk}} / 2^k \tag{5}$$

## åicest 2016

Advantages and disadvantages of using DDS method for managing resonant inverters are:

- > Working in a wide frequency range max  $\frac{1}{2}$  fin.

- A very small step of frequency variation  $-\Delta f$ .

- Easy to implement digital matched filter.

### **Disadvantages:**

- The main disadvantage is the phase noise, its value reaches 1/f, at fout=1/2fin.

- Requires large program capacity.

### Increment/decrement counter

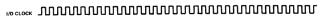

This is a bias scaler, whose amendment is managed by two entrances carry and borrow - fig.5.

The resulting output frequency (I/Dout) of I/D counter – is  $\frac{1}{2}$  I/Dclk. It may be amended "up" or "down" depending on which input is received 1-0 transition. The amendment is obtained by adding or deleting  $\frac{1}{2}$  cycle. To reduce the phase noise can be used an additional counter (divisor N), then phase noise will be reduced by 1/N.

Advantages and disadvantages in using this method are:

- ▶ Relatively small step of frequency variation  $-\Delta f$  (tens of Hz).

- Small phase.

### Disadvantages:

- Complex to implement digital filter

- Limited range of frequency variation

- Dependence on many parameters.

### Loop filters.

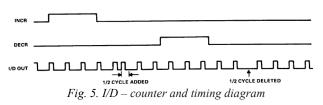

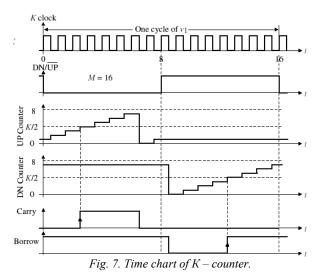

The task of the filters is to convert the signal so that it is convenient to control the synthesized oscillator. Depending on the digital synthesized adjustable generator are used various filters. If the used generator is I/D – counter, then a filter that converts the signal phase difference from the phase detector in the number of pulses is needed. Thus plays the role of an integrator [8]. Such a filter can be realized by a reversible counter with an adjustable division ratio, called K-counter -Fig. 6. The principle is explained with tim diagrams shown in Fig. 7. The number of output pulses (transfers) is proportional to the operating time of the respective counter UP or DOWN, respectively, and the phase difference.

Fig. 6. Programmable frequency divider of K - counter.

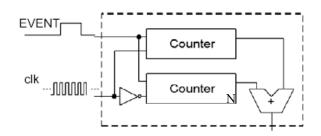

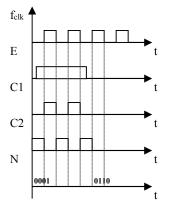

Another type of filter is converter of time into a digital code. The resulting code (word) N directly operates the generator - DDS or Fraction-N, changing its output frequency proportional to the code N. The condition for synthesis of the converter is  $f_{clk} >> EVENT$

Fig. 8. Converter time numerical code.

Fig. 9. Time chart of converter - time in numerical code.

### <u>å icest 2016</u>

Between the considered options are development and synthesized PLL scheme with DDS generator and filter T2C (time to code converter) in CPLD Xilinx CoolRunner2.

The experimental object for management is a transistor half-bridge parallel inverter, which is running with frequency above the resonance one. The input power of the converter is P = 1,6 kW. Load capacitance value is C = 1,72 µF. It is implemented with non-inductive capacitors. The load inductance - the inductor has a value L = 3,1 µH, wound copper tube with a diameter of 9 mm with 13 windings. The diameter of the inductor is 73 mm.

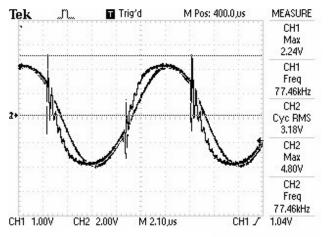

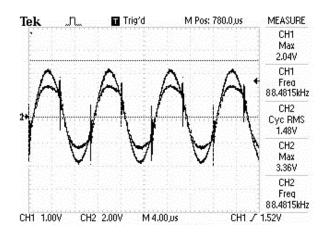

A study of system performance under different input power and loads has been made. On Fig. 10 a) is shown the current and voltage in resonance at low load and input voltage E = 130V and input current I = 12,3A. On the channel one of the oscilloscope is visualized the form of the current and on the channel two the form of the voltage. Both signals were observed after the transformers for feedback. It can be seen that the mode of the inverter is good, when the frequency is maintained by digital PLL. The increase of the input voltage leads to bigger power load. This will lead to its heat and therefore to change the parameters of the circle and therefore the frequency will start to decrease.

Fig. 10 - A) Voltage on the parallel circuit and the current - hollow material.

Fig. 10 - B) Voltage on the parallel circuit and the current - dense material.

At higher load (when solid material is used), the operating frequency is changed on 88,48 kHz - Fig. 10 b). Input voltage E = 122V, I = 10,7 A.

#### **III.** CONCLUSION

The analysis shows that the best results are achieved when synthesized management scheme with 16bit DDS generator is used. A 16 bit counter for filter, which converters signal from the phase detector is realized. The response time of the system as a whole depends on the sparsity of the filter and the time of integration. Time integration is proportional to the signal EVENT - phase difference. Under the process of locking frequency (resonance inverter) phase deviation is small and therefore the reaction has several clock cycles. Great importance has the supporting clocked. Although the inverter operates at frequency. Thus the influence of phase noise is minimized.

Good results are achieved also when I/D counter is used, but the digital filter is more complex and requires more programmable logic resources.

Using methods for fully digital control improved adaptability to any electronic system, provide much easier monitoring of parameters and setting of such microcontrollers.

### REFERENCES

- [1] Donchev B., M. Hristov, P. Goranov, *Design of control system* for inductive heating converter, ET 2001, Sozopol, Bulgaria.

- [2] Olsson T., and P. Nilsson. A Digital PLL made from Standard Cells", Proceedings of the 15 th European Conference on Circuit Theory and Design In Proceedings of ECCTD' 01, Helsinki University of Technology, Finland 28 th–31 st August 2001, pp. 277 – 281.

- [3] Goranov G., Digital synthesis of PLL for control induction heating inverters, ISC Electronics 2004 pp. 39 44.

- [4] Denny Ambramovitch, Lyapunov Redesign of Classical Digital Phase-Locked Loop, Communication and Optical Research Lab 2003;

- [5] Analog Devices, Fractional-N Frequency Synthesizer ADF41xx, 2006.

- [6] В.Майская, "Fractional N Синтезаторы" ЭЛЕКТРОНИКА: Наука, Технология, Бизнес, стр. 10 -16, бр.5, 2002.

- [7] Maini, A.K., "Digital Electronics Principles, Devices and Applications", John Wiley & Sons Ltd, ISBN: 978-0-470-03214-5, Chichester, England, 2007;

- [8] Thomas Olsson, Peter Nilsson, A Digital PLL made from Standard Cells, Lund University, Dept. of Electroscience, Sweden 2001.