# Functional and Timing Analysis of Improved Serial Pseudorandom/Natural Code Converter

Goran Miljković<sup>1</sup>, Dragan Denić<sup>2</sup>, Milan Simić<sup>3</sup> and Aleksandar Jocić<sup>4</sup>

Abstract – The pseudorandom/natural code converters are often part of systems and components which exploit pseudorandom binary code, such as absolute pseudorandom position encoders. Serial pseudorandom/natural code converters have advantage in simplicity of hardware implementation, but their conversion time is greater compared to parallel code converters. In the paper is applied Galois generator in the implementation of serial pseudorandom/natural code converter in order to reduce conversion time. One faster way for adjustment logic design which is necessary for proper functioning of Galois based serial code converter is proposed. It is detailed described functionality of serial code converter through simulation examples in NI Multisim software. Also, detailed timing analysis of Fibonacci and Galois based serial pseudorandom/natural code converter is given.

Keywords – pseudorandom binary sequence (PRBS), pseudorandom/natural code converter, Fibonacci and Galois architecture for generation of PRBS code

## I.Introduction

The absolute pseudorandom position encoders are wellknown digital transducers which could be used for absolute position measurement in industry, robotics, electrical power engineering, elevators, telescopes/antennas, printers, etc. Absolute position determination in these encoders is based on property of *n*-bit pseudorandom binary sequence (PRBS) that sliding window of length n, which passes along a sequence, will extract unique code word in every moment [1, 2]. Also, the code words are now longitudinally lined, and two successive code words are overlapping and differ only in one bit. The PRBS signal is exploited in other fields, cryptography, telecommunications, testing of VLSI circuits [3], testing of gas sensors [4], measurement of the frequency response, etc. The absolute pseudorandom position encoder consists from following functional parts: code reading system [2, 5], code scanning [2, 6, 7], error detection [8] and pseudorandom/natural code conversion [2, 9, 10].

The pseudorandom/natural code conversion method is

<sup>1</sup>Goran Miljković is with the Faculty of Electronic Engineering at University of Niš, Aleksandra Medvedeva 14, 18000 Niš, Serbia, Email: goran.miljkovic@elfak.ni.ac.rs

<sup>2</sup>Dragan Denić is with the Faculty of Electronic Engineering at University of Niš, Aleksandra Medvedeva 14, 18000 Niš, Serbia, Email: dragan.denic@elfak.ni.ac.rs

<sup>3</sup>Milan Simić is with the Faculty of Electronic Engineering at University of Niš, Aleksandra Medvedeva 14, 18000 Niš, Serbia, Email: milan.simic@elfak.ni.ac.rs

<sup>4</sup>Aleksandar Jocić is with the Faculty of Electronic Engineering at University of Niš, Aleksandra Medvedeva 14, 18000 Niš, Serbia, Email: <u>aleksandar.jocic@elfak.ni.ac.rs</u>

compromise between two opposite requests, minimal conversion time and low complexity and price of used hardware. The different pseudorandom/natural code conversion methods can be sorted to three distinct groups: parallel [7], serial [2, 9] and serial-parallel [7]. The parallel pseudorandom/natural code conversion is the fastest, but requests large ROM memory for storing of code conversion table especially in the case of high resolution encoder. The serial pseudorandom/natural code conversion is simplest, less hardware expensive, but slower method. The compromise solution is the serial-parallel code converter, which combines previous two methods.

In the paper are detailed described improved solution of serial pseudorandom/natural code converter based on Galois generator of PRBS which can be used in absolute pseudorandom position encoder or in other fields where PRBS is applied. The presented serial pseudorandom/natural code converter is then implemented in software NI Multisim, integrated capture and simulation design environment. These simulations are used for functional and timing analysis of serial pseudorandom/natural code converters.

# II. IMPROVED SERIAL PSEUDORANDOM/NATURAL CODE CONVERTER

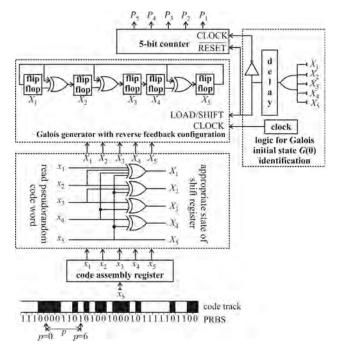

Duration of pseudorandom/natural code conversion process, the conversion time, becomes critical at high resolution absolute pseudorandom position encoders. The serial pseudorandom/ natural code converters are based on the fact that is possible to find the actual value of the position p by counting of the steps that shift register with reverse feedback needs until it reaches the initial state by successive shifting from the read pseudorandom n-bit code word. One solution is the serial pseudorandom/natural code converter based on Fibonacci generator [9]. Improved solution is based on faster Galois generator of PRBS which can be used in serial code converter instead of Fibonacci generator [9]. This generator also uses a shift register, the content of which is modified at every step by a binary-weighted value of the output stage, using XOR gates. The improved solution of serial pseudorandom/natural code converter based on Galois generator can be seen in Fig. 1. A 31-bits long PRBS generated by a 5-bit shift register with the feedback set for direct generation law [5,4,3,1] is used for the encoding of the track. It consists of the following 11100001101010010001011111101100. pseudorandom code bits with one code reading head  $x_5$  are loaded into five-cell bidirectional code assembly register. The actual content of the code assembly register corresponding to the current position is loaded into a shift register of Galois generator.

Fig. 1. Serial pseudorandom/natural code converter based on Galois generator

This solution is faster because it has reduced number of logic gates (XOR gates) in the feedback loop. The position of XOR gates between flip flops in the Galois shift register is determined by the used feedback set [5,4,2,1] for reverse generation law. Adequate feedback sets for different resolutions of PRBS sequence can be found in the literature [10]. Now, one XOR gate exists in the feedback configuration compared to three serial connected XOR gates in the case of Fibonacci generator. But, the additional logic that read code word converts to the appropriate content of the shift register is needed for proper functioning of this converter. This logic only participates on the beginning of each code conversion cycle and does not further participate in the code conversion process. The 5-bit counter and additional logic for Galois initial state G(0) identification are also needed in this serial pseudorandom/natural code converter.

Logic for initial adjustment of read pseudorandom code word is needed because the read n-bit pseudorandom code word in real time is not identical to the n-bit current content of the shift register, which was the case at Fibonacci generator. Procedure of this adjustment logic design is detailed explained in the reference [9] for n=5 bit resolution and chosen feedback set. Following this procedure for logic design in the case of resolution n=5 and feedback set for Galois generator [5, 4, 2, 1], the following set of equations is obtained:

$$X_5 = x_5 \tag{1}$$

$$X_4 = x_4 \oplus x_5$$

(2)

$$X_3 = x_3 \oplus x_4$$

(3)

$$X_3 = x_3 \oplus x_4 \tag{3}$$

$$X_2 = x_2 \oplus x_3 \oplus x_5 \tag{4}$$

$$X_1 = x_1 \oplus x_2 \oplus x_4 \oplus x_5 \tag{5}$$

Based on the previous logic equations (1) to (5) the following matrix can be written:

|                                   | $X_5$ |   |   |   | $x_1$ |

|-----------------------------------|-------|---|---|---|-------|

| g 55 X₅                           | 1     | 0 | 0 | 0 | 0     |

| å .≯ X₄                           | 1     | 1 | 0 | 0 | 0 0 0 |

| $X_3$                             | 0     | 1 | 1 | 0 | 0     |

| $\sim X_2$                        | 1     | 0 | 1 | 1 | 0     |

| $\mathfrak{S} = X_{\mathfrak{l}}$ | 1     | 1 | 0 | 1 | D     |

where columns are in order  $\{x_5, x_4, x_3, x_2, x_1\}$ , and rows in order  $\{X_5, X_4, X_3, X_2, X_1\}$ . It can be seen that for coefficients [5, 4, 2, 1] in rows, the adequate diagonals are filled with "1" beginning from defined coefficients. It is highlighted diagonal filled with "1" for coefficient 5 in the feedback set. So, for any feedback set of coefficients this matrix can be easily written, and then from there adequate equations for adjustment logic can be easy obtained.

This procedure is checked for different resolutions from 3 to 16 bit, and various possible feedback sets [10]. Based on previous considerations it is confirmed that exist the clear rule for matrix filling for any chosen resolution and the feedback set. The numbers in feedback set defines adequate starting position in rows,  $X_1$ , ...,  $X_n$ , from which starts with filling of diagonals with "1". Filled matrix directly gives set of logic equations which is needed for design of adequate logic for initial adjustment of read pseudorandom code word. This logic directly converts current content of Fibonacci shift register to adequate content of Galois shift register in adequate PRBS generator.

# III. SIMULATIONS AND ANALYSIS OF SERIAL **CONVERTERS**

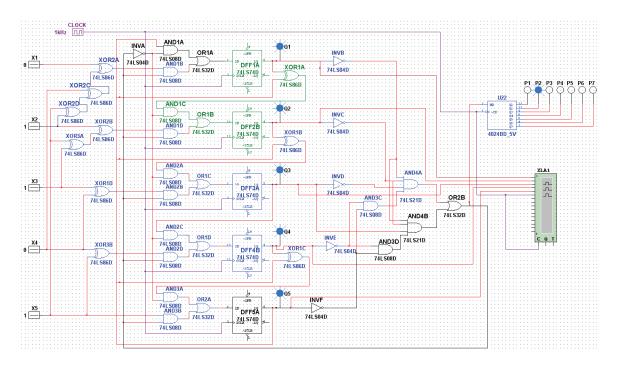

For purpose of detailed functional and timing analysis of presented solution of serial pseudorandom/natural code converter, simulation of hardware realization is performed in software environment NI Multisim 11.0, Fig. 2. In Multisim software can be fund several useful tools and parts for digital circuits. They range from digital gates (both families, TTL and CMOS are supported), indicators (such as LED's, LCD displays, Logic Analyzers and Word Generators), wires, data buses and power supplies. The most widely used subfamily for digital circuit simulation is the 74LSXX series where the digits after the LS indicate the gate's function. This subfamily simulation of presented pseudorandom/natural code converters, and applied logic gates in the simulations with their propagation delays are listed in Table 1.

Table 1. Logic gates and adequate propagations delays

| Logic gates       | Used logic gates<br>from 74LSXX series | Propagation delays               |

|-------------------|----------------------------------------|----------------------------------|

| AND               | 74LS08D                                | 15 ns                            |

| OR                | 74LS32D                                | 22 ns                            |

| INV               | 74LS04D                                | 15 ns                            |

| XOR               | 74LS86D                                | 30 ns                            |

|                   |                                        | $t_s=20 \text{ ns}$              |

| D flip flop       | 74LS74D                                | $t_{\rm h}=5~{\rm ns}$           |

|                   |                                        | $t_{\text{CLK-Q}}=25 \text{ ns}$ |

| AND with 4 inputs | 74LS21D                                | 15 ns                            |

Fig. 2. Simulation of serial pseudorandom/natural code converter based on Galois generator in Multisim

The conversion process is executed for concrete example of read pseudorandom code word and for defined initial code word. 7-bit binary counter is used for counting of needed steps to shift register for finishing of one code conversion cycle. The read 5-bit code word  $x=x_1x_2x_3x_4x_5$  is loaded in the 5 D flip flops on the beginning of the code conversion process. It is used example where read pseudorandom code word is  $x = \{0,1,1,0,1\}$ , and initial code word is  $X(0) = \{1,1,1,0,0\}$ . It is needed six clock periods to the shift register when its state becomes equal to the initial state, which is output of the binary counter in the case of Fibonacci generator. In the case of Galois based code converter, Fig. 2, the read pseudorandom code word  $x=\{0,1,1,0,1\}$  is firstly converted to appropriate state of the Galois shift register  $X_{\text{appr.state}} = \{0,1,1,1,1\}$  based on equations (1)-(5), and then is also needed six clock periods to the shift register when its state becomes equal to Galois initial state  $G(0) = \{0,0,1,0,0\}$ . Galois initial state is obtained from initial state  $X(0)=\{1,1,1,0,0\}$  using equations (1)-(5). It is proved proper functioning of proposed hardware realization for different examples of read and initial pseudorandom code words. States of the shift register in Fibonacci and Galois generator in each clock period during shifting from read pseudorandom code word to the initial code word of presented example are listed in Table 2. In the simulations of serial converter, Fig. 2, is also used AND gate with 4 inputs together with one AND gate for initial state identification.

To find the maximal working frequency of the whole digital circuit, which is the most significant difference between two presented solutions, it is needed to analyze propagation delays of each path. Combinational propagation delays are additive. It is possible to determine the propagation delay of a larger combinational circuit by adding the propagation delays of the circuit components along the longest path. Frequency must be determined by locating the longest path among all the flip-flop paths in the circuit.

Table 2. Shift register content in Fibonacci and Galois generator

| Output of the binary counter     | Fibonacci<br>generator shift<br>register content:<br>{X <sub>1</sub> X <sub>2</sub> X <sub>3</sub> X <sub>4</sub> X <sub>5</sub> } | Galois<br>generator shift<br>register content:<br>{X <sub>1</sub> X <sub>2</sub> X <sub>3</sub> X <sub>4</sub> X <sub>5</sub> } |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Read pseudorandom code word, P=0 | 01101                                                                                                                              | 01111                                                                                                                           |

| P=1                              | 00110                                                                                                                              | 11010                                                                                                                           |

| P=2                              | 00011                                                                                                                              | 01101                                                                                                                           |

| P=3                              | 00001                                                                                                                              | 11011                                                                                                                           |

| P=4                              | 10000                                                                                                                              | 10000                                                                                                                           |

| P=5                              | 11000                                                                                                                              | 01000                                                                                                                           |

| Initial code word, P=6           | 11100                                                                                                                              | 00100                                                                                                                           |

Propagation delays along longest paths in both simulations are (Fig 2.):

- for Fibonacci based converter (from the output of the fifth flip flop DFF5A, through three XOR gates in the feedback loop, then AND1A, OR1A, to the input of the first flip flop DFF1A):

$T_1 = t_{\text{CLK-Q}}(5) + 3 t_{\text{pd}}(\text{XOR}) + t_{\text{pd}}(\text{AND}) + t_{\text{pd}}(\text{OR}) + t_{\text{s}}(1) = 25 \text{ ns} + 3 \times 30 \text{ns} + 15 \text{ ns} + 22 \text{ ns} + 20 \text{ ns} = 172 \text{ ns},$

- for Fibonacci based converter (from the output of the fifth DFF5A, through logic for initial state identification INVF, AND3D, AND4B, OR2B, INVA, then AND1A, OR1A to the input of the first flip flop DFF1A):

$T_2 = t_{\text{CLK-Q}}(5) + t_{\text{pd}}(\text{INV}) + 2 t_{\text{pd}}(\text{AND}) + t_{\text{pd}}(\text{OR}) + t_{\text{pd}}(\text{INV}) + t_{\text{pd}}(\text{AND}) + t_{\text{pd}}(\text{OR}) + t_{\text{s}}(1) = 25\text{ns} + 15\text{ns} + 2x15\text{ns} + 22\text{ ns} + 15\text{ ns} + 15\text{ ns} + 22\text{ ns} + 20\text{ ns} = 164\text{ ns}.$

So, maximal working frequency of Fibonacci based converter would be,

$$f_{\text{max-fibonacci}} = 1/T_1 = 5.81 \text{MHz}.$$

(6)

- for Galois based converter (from the output of the first flip flop DFF1A, through one XOR gates in the feedback loop XOR1A to the input of the second flip flop DFF2B):

$$T_3 = t_{\text{CLK-Q}}(5) + t_{\text{pd}}(\text{XOR}) + t_{\text{pd}}(\text{AND}) + t_{\text{pd}}(\text{OR}) + t_{\text{s}}(1) = 25 \text{ ns} + 30 \text{ns} + 15 \text{ ns} + 22 \text{ ns} + 20 \text{ ns} = 112 \text{ ns}$$

-  $T_2$  is the same as in the case of the Fibonacci based converter, so maximal working frequency of Galois based converter would be,

$$f_{\text{max-galois}} = 1/T_2 = 6.09 \text{MHz} \tag{7}$$

From previous timing analysis, it can be concluded that Galois generator is faster than Fibonacci. The pseudorandom/natural code converter based on Galois generator has additional propagation delay due to the logic for initial conversion of read pseudorandom code word which is equal to propagation delay of three serial connected XOR gates (XOR2A, XOR2C, and XOR2D). Also, the contamination delays along each path are greater than or equal to the destination flip flop hold time, so the circuit will operate as designed.

For presented example of 5-bit pseudorandom binary sequence, 31 unique pseudorandom code words define absolute position. So, for the worst case, if the code converter needs 30 clock periods to convert the read pseudorandom code word in relation to the initial pseudorandom code word which present zero position, maximal duration of one conversion cycle for Fibonacci and Galois generator would be,

$$T_{\text{conv-fibonacci}} = 30 \text{x} \, 1/f_{\text{max-fibonacci}} = 5.16 \mu \text{s}$$

(8)

$$T_{\text{conv-galois}} = 3x \ t_{\text{pd}}(\text{XOR}) + 30x1/f_{\text{max-galois}} = 5.01 \mu \text{s}$$

(9)

So, the serial pseudorandom/natural code converter based on Galois generator is relatively faster than Fibonacci based for,

$$\delta_{\%} = \frac{T_{conv-fibonacci} - T_{conv-galois}}{T_{conv-fibonacci}} 100\% = \frac{5.16 - 5.01}{5.16} 100\% = 2.9\%$$

(17)

Duration of code conversion time depends on used resolution of PRBS and used feedback set (for same resolution different feedback sets exist, with different number of coefficients).

# IV. CONCLUSION

Improved, Galois based implementation of serial pseudorandom /natural code converters is presented and analyzed. It is proved reducing of conversion time at Galois based serial converter, which is its main advantage, by using detailed timing analysis. It is examined full functionality of both, Fibonacci and Galois based serial converters through simulation in NI Multisim software. The solution for easier designing of necessary logic for initial adjustment of read pseudorandom code word at Galois based converter is also given.

#### ACKNOWLEDGEMENT

Research activities presented in this paper, are supported by funds of the Ministry of Science and Technological Development of Republic of Serbia, having the reference project number TR32045.

### REFERENCES

- F.J. MacWilliams, N.J.A Slone, "Pseudo-random sequences and arrays", Proceeding of IEEE, Vol. 64, No. 12, pp. 1715-1728, 1976.

- [2] E. M. Petriu, J. S. Basran, "On the position measurement of automated guided vehicles using pseudorandom encoding", in IEEE Trans. IM, vol. 38, no. 3, pp. 799-803, 1989.

- [3] J.C. Rau, P.H. Wu, Y.F. Ho, "A novel reseeding mechanism for improving pseudo-random testing of VLSI circuits", in Tamkang Journal of Science and Engineering vol. 11, no. 2, pp. 175-184, 2008.

- [4] M.E.H. Amrani, R.M. Dowdeswell, P.A. Payne, K.C. Persaud, "Pseudo-random binary sequence interrogation techniques for gas sensors", in Sensor. Actuat. B-Chem. vol. 47, pp. 118-124, 1998.

- [5] M. Arsić, D. Denić, "New pseudorandom code reading method applied to position encoders", in Electron. Lett. vol. 29, pp. 893-894, 1993.

- [6] D. Denić, G. Miljković, "Code reading synchronization method for pseudorandom position encoders", in Sensor. Actuat. A-Phys. vol. 150, pp. 188-191, 2009.

- [7] E.M. Petriu, J.S. Basran, F.C.A. Groen, "Automated guided vehicle position recovery", in IEEE Trans. Instrum. Meas. vol. 39, pp. 254-258, 1990.

- [8] D. Denić, M. Arsić, "Checking of pseudorandom code reading correctness", in Electron. Lett. vol. 29, pp. 1843-1844, 1993.

- [9] D. Denić, I. Stojković, "Pseudorandom/natural code converter with parallel feedback logic configuration", in Electron. Lett. vol. 46, pp. 921-922, 2010.

- [10] New Wave Instruments, "Linear feedback shift registers: Implementation, M-sequence properties, feedback tables", (2004).

http://www.newwaveinstruments.com/resources/articles/m\_sequence\_linear\_feedback\_shift\_register\_lfsr.htm