# Studying the short channel effect in MOSFET Transistor **Amplifiers**

## Stoycho Manev

Abstract - The presented paper is aimed toward educationalmethodological purposes. The short channel effects in MOSFET Transistors are investigated. PSPICE simulation of circuits, containing MOSFET Transistors are performed.

Keywords - short channel effect, MOSFET Transistors, Analog circuits

## I. Introduction

The presented paper is aimed toward educationalmethodological purposes. The contemporary high level of miniaturization requires that by the electronic design all possible factors should be considered. The short channel effects are very widespread in MOSFET devices. They can be summarized in the following directions[1]: channel length modulation; threshold voltage roll-off; narrow gate width effects; reverse short channel effects; punch through; mobility degradation; velocity saturation[1].

## II. THEORETICAL BACKGROUND

A. Classification of the MOSFET Transistors

In Fig.1 is presented the perspective projection of MOSFET Transistor[2]

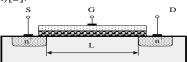

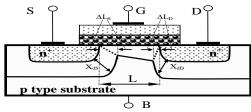

Fig. 1. MOSFET Transistor (perspective projection) In Fig.2, is shown a long-channel MOSFET Transistor (cross section)[2].

Fig. 2. Long-channel MOSFET Transistor(cross section) If the channel length  $L \gg sum$  of the depletion widths of the drain and the source, as shown on Fig.2, the MOSFET Transistor is classified as long-channel [1],[2].

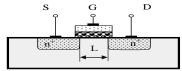

Contrariwise, if L is comparable with the sum of the source and drain depletion widths, as presented on Fig.3 the MOSFET Transistor is classified as short-channel [1],[2].

Fig. 3.Short-channel MOSFET Transistor(cross section) B. Basic mathematical equations[3]

<sup>1</sup>Stoycho Manev is with the Faculty of Telecommunications at Technical University of Sofia, 8 Kl. Ohridski Blvd, Sofia 1000, Bulgaria EMAIL: smanev@tu-sofia.bg

a) In the triode area the equation (1) is valid [3]:

$$I_{D0} = \mu_n . C_{ox} . \frac{W}{L} . \left[ (V_{GS} - V_{th0}) . V_{DS} - \frac{V_{DS}^2}{2} \right], \tag{1}$$

where [3],[1]: I<sub>D0</sub> designates the value of the drain current, ignoring the effect of the channel length modulation;  $C_{ox}$  is the gate oxide capacitance per unit area;  $V_{\it th0}$  is the threshold voltage;  $\mu_{\scriptscriptstyle n}$  is the field effect mobility of electron[1];  $V_{\scriptscriptstyle DS}$ is the voltage drain-source;  $V_{GS}$  is the voltage gate-source.

b) In the saturation area [3]:

$$I_{D0} = \frac{\mu_n \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot (V_{GS} - V_{th0})^2 \qquad (2)$$

The transconductance can be calculated by means of the

$$g_{m} = \mu_{n}.C_{ox}.\frac{W}{L}.(V_{GS} - V_{th0}) = \sqrt{2.\mu_{n}.C_{ox}.\frac{W}{L}.I_{D0}}$$

(3)

\* Channel length modulation [3]

By channel length modulation the equations (1) and (2), concerning the drain current in triode area and in the saturation area, can be presented as follows[3]:

$$I_D = (1 + \lambda . V_{DS}) . I_{D0} \tag{4}$$

where  $\lambda$  is semi empirical constant.

\* Threshold voltage roll off [2]

The threshold voltage of short-channel N - MOSFET Transistor is less than the corresponding threshold voltage of the long - channel MOSFET Transistor. It can be calculated by means of the relation [2]:

$$V_{th0 \ short \ channel} = V_{th0 \ long \ channel} - \Delta V_{th0}, \tag{5}$$

where:

$$\Delta \mathbf{V}_{\text{th}\theta} = \frac{I}{\mathbf{C}_{\text{ox}}} . \sqrt{2.\mathbf{q}.\boldsymbol{\varepsilon}_{\text{Si}}.\mathbf{N}_{\text{A}} \left| -2.\boldsymbol{\phi}_{\text{f}} \right|} . \frac{\mathbf{x}_{\text{j}}}{2.\mathbf{L}} . \left[ \left( \sqrt{I + \frac{2.\mathbf{x}_{\text{dS}}}{\mathbf{x}_{\text{j}}}} - I \right) + \left( \sqrt{I + \frac{2.\mathbf{x}_{\text{dD}}}{\mathbf{x}_{\text{j}}}} - I \right) \right] [2]$$

$$(6)$$

Here [2]:  $x_{dS}$  is the depth of the depletion region at source;  $x_{dD}$  is the depth of the depletion region at drain;  $N_A$  is the substrate doping density;  $\phi_f$  is the substrate Fermi potential;  $\boldsymbol{\varepsilon}_{Si}$  is the dielectric constant of silicon;  $\boldsymbol{q}$  is the electron charge;  $C_{ox}$  is the gate oxide capacitance per unit area;  $x_i$  is the junction depth. The depletion regions are detailed presented on Fig.4[2]:

Fig. 4.MOSFET Transistor structure (cross section) \* Punch through[3]

When the depletion region at source  $X_{dS}$  and the depletion region at drain  $X_{dD}$  merge there is a punch through. The drain current cannot be driven by gate voltage.

## \* Velocity saturation[3]

In order to realize ever smaller in size devices modern technologies have been applied. In this case high-field effects must be taken into account. In this analysis essential is the effect of velocity saturation. In silicon the electron drift cease to depend from the applied electric field at value approximately  $10^6$  V/m and saturates at a value of approx.  $10^5$  m/s. The result, obtained from the expression:  $\frac{V_{GS} - V_{tho}}{I}$

plays an important role by the short-channel effects. In case, that  $\frac{V_{GS} - V_{\text{th0}}}{L}$  approaches  $E_{\text{sat}}$ , where  $E_{\text{sat}}$  is typical

approximately  $4.10^6 V/m$ ,  $I_D$  is not more dependent from L. It's value becomes:

$$I_{D} = \frac{\mu_{n.} C_{ox}}{2} .W. (V_{GS} - V_{th0}) .E_{sat} [3]$$

(7)

The velocity saturation leads to restriction of the value of the transconductance:  $g_m = \mu_n \cdot C_{ox} \cdot \frac{W}{2} \cdot E_{sat}$  [3] (8)

For its part the transit frequency  $\omega_T$  can be expressed as follows:  $\omega_T \approx \frac{3}{4} \cdot \frac{\mu_n \cdot E_{sat}}{I}$  [3] (9)

The reverse short-channel effects are related to the doping profile of the analyzed MOSFET device[3]

#### \* Narrow channel width effects[2]

Considerations about the channel width: the analysis is similar to the analysis, concerning the channel length. If the channel width W is comparable with the maximum depletion regions thickness into the substrate  $(x_{dm})$ , the MOSFET Transistor can be classified as narrow-channel. The narrow channel effect leads to increase of the threshold

$$V_{th\theta \ narrow \ channel} = V_{th\theta \ long \ channel} + \Delta V_{th\theta}$$

(10)

In case that the shape of the depletion regions edges are modeled by means of quarter circular arcs the following expression is valid [2]:

$$\Delta V_{th0} = \frac{1}{C_{ox}} \cdot \sqrt{2.q.\varepsilon_{Si} \cdot N_A \left| -2.\phi_f \right|} \cdot \frac{\pi \cdot x_{dm}}{2.W}$$

(11)

## \* Mobility degradation[3]

voltage [2]:

The increase of the gate potential leads to decrease of the mobility of the charge carriers. This effect can be quantitative evaluated by means of the normal field mobility degradation factor  $\theta$ . It has a typical value in the range:  $(0,1 \div 1) V^{-1}$  and is inversely proportional to the gate

oxide thickness. In order to obtain the actual value of the drain current  $I_D$  the calculated value must be multiplied by[3]:  $\frac{1}{1 + \theta \cdot (V_{GS} - V_{th0})}$  (12)

## III. PSPICE MODELS OF THE ANALYZED CIRCUITS

In traditionally courses the focus of the analysis of the MOSFET devices is aimed toward the basic characteristics. In this paper special attention is turned on the short channel effects in MOSFET Transistors.

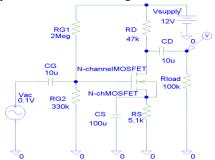

The circuit, which has been used in the presented paper for AC analysis, is shown on the Figure bellow.

Fig. 5.PSPICE model for AC analysis

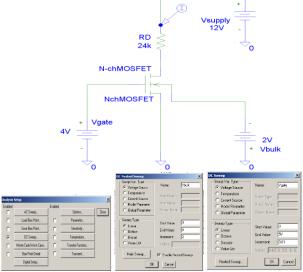

The circuit for analysis of mobility degradation and the dependence on the oxide thickness is displayed on Fig.6. In order to study the roll-off effect the circuit, presented on Fig.6, is used.

Fig. 6.PSPICE model for studying the "roll-off" effect

The PSPICE models of the transistors in these circuits are based on the Level 3 PSPICE parameters, given in [3].

The narrow gate width effects have been investigated by means of the both circuits (shown on Fig.5 and Fig.6).

The channel length modulation has been examined using the PSPICE MOSFET parameters Level 2, presented in [4].

As it can be seen from the analysis setup conditions concerning the circuit, presented on Fig.6, DC nested sweep has been activated. The gate voltage changes in the range:  $0V \div 5V$  while the bulk voltage vary from 0V to 8V by step of increment 2V.

#### IV. IMULATION RESULTS AND ANALYZES

#### A Mobility degradation

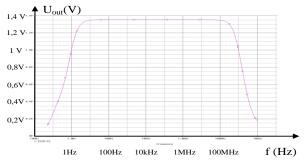

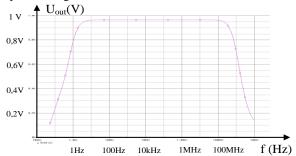

The simulation experiments, concerning the AC analysis, have been done by mobility degradation factor  $\theta$  (THETA) = 2,3.10<sup>-1</sup>, as given in [3]. The results are presented on Fig.7.

Fig.7.AC analysis by  $\theta$  (THETA) = 2,3.10<sup>-1</sup>

The circuit, displayed on Fig.5, has been used by the simulation. Changing the value from  $\theta = 2,3.10^{-1}$  to  $\theta = 1$  leads to consequent change in the AC characteristic. This is displayed on Fig.8.

Fig.8. AC analysis by  $\theta$  (THETA) = 1

As expected, taking into account the analytical expression (12), from the Figures above, becomes obvious that the output voltage is inverse proportional to the value of  $\,\theta$ .

By the both simulations the value of the oxide thickness is  $9.5.10^{-9}$ .

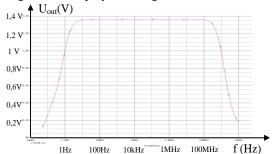

## B Influence of the oxide thickness

In order to establish qualitative relationship between this thickness and the AC parameters of the MOSFET amplifier another simulation has been performed.

Changing the oxide thickness from 9,5. 10<sup>-9</sup> to 3.10<sup>-9</sup> the following results, displayed on Fig.9, are obtained.

Fig.9. AC analysis by oxide thickness  $3.10^{-9}$ ,  $\theta=2,3.10^{-1}$  All simulations up to here have been done by:  $L=2\mu m$  and  $W=16~\mu m$ .

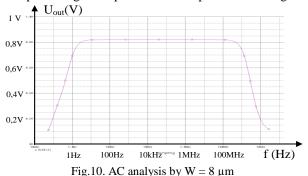

## C Narrow channel width effects

In order to analyze the narrow gate width effects the value of W has been reduced to  $8\mu m$ . The value of L remains  $2 \mu m$ ,  $\theta = 2,3.10^{-1}$ , the oxide thickness is  $9,5.10^{-9}$ . Taking into account the equations: (1), (2), (3) decrease of the output voltage is expected. This is presented on Fig.10.

The graphical results, shown on Fig.10, confirm these expectations.

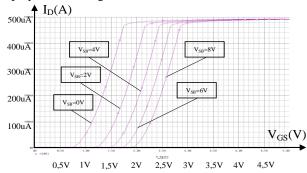

#### D Roll off effects

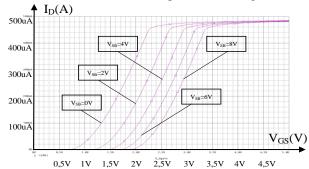

The investigations, concerning the roll-off effects, have been performed by means of the circuit, presented on Fig.6. The simulation results, done by  $L=2\mu m,\ W=16\mu m,$  are displayed on the Figure bellow.

$\label{eq:Fig.11.Characteristic ID-VGATE} Fig.11. Characteristic ID-VGATE} by L = 2\mu m, W = 16\mu m$  The change of the bulk voltage toward more negative values leads to subsequent translation of the characteristic ID-UGATE to the right, as it becomes obvious from Fig.11.

#### a) Narrow channel width effects

According to expressions (11),(10) the reduction of width W to 8um leads analytically to increase of the threshold voltage. By initial conditions L=  $2\mu m$  W =  $8\mu m$  simulations have been done. The results are presented on Fig.12.

Fig.12. Characteristic  $I_D$  -  $V_{GS}$  by  $L=2\mu m$ ,  $W=8\mu m$  Comparing the characteristics from Fig.11 and Fig.12 the increase of the threshold voltage can distinctly be seen.

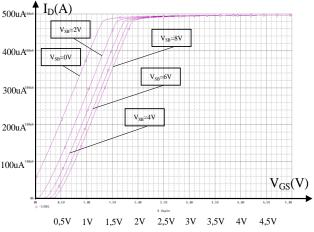

#### b) Short channel effects

While the width W reduction leads to increase of the threshold voltage, according to expressions (6) and (5), the supposedly decrease of the channel length L should cause increase of  $\Delta V_{th0}$  and subsequent decrease of the threshold voltage  $V_{th0\,short\,channel}$ . Simulations using PSPICE model attributes L = 0,5 µm, W = 8 µm have been done. The obtained results are presented on Figure 13.

Fig.13. Characteristic  $I_D$  -  $V_{GS}$  by  $L=0.5\mu m,\,W=8\mu m$

The translations of the characteristics to the left, compared to the characteristics, displayed on Fig.12, confirm the expected effect of decrease of the threshold voltage.

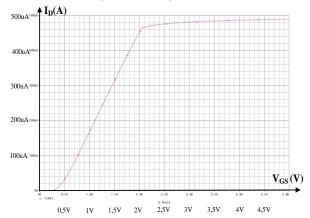

#### E Channel length modulation

By the simulations the PSPICE model, proposed in [4], has been used. The values of  $V_{SB}$  , L and W have been set to:  $V_{SB}=2V,\,L=2\mu m$  ,  $W=16\mu m$  .

Fig.14. Characteristic  $I_D$  -  $V_{GS}$  by  $\lambda = 3{,}903.10^{-2}$

The graphical results, shown above, concern the PSPICE model parameter values, given in [4]. The value of  $\lambda$  (LAMBDA), given there, is 3,903.10<sup>-2</sup>. In order to study the influence of the value of parameter  $\lambda$  upon the drain current, which analytically is described by means of expression (4), another value of  $\lambda$  has been inserted in the PSPICE model

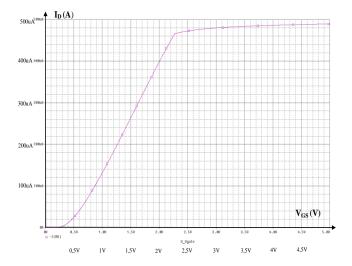

of the MOSFET Transistor. In this case  $\lambda$  has been set to value of  $\,1.10^{\text{-}2}.$

Fig.15. Characteristic I<sub>D</sub> - V<sub>GS</sub> by  $\lambda = 1.10^{-2}$

An essential change in the slope of the characteristic  $I_D$  -  $V_{GS}$ , displayed on Fig.15, in comparison with the slope of the characteristic  $I_D$  -  $V_{GS}$ , presented on Fig.14, has been found out. This fact is in accordance with the analytical expression, concerning  $I_D$ , given in (4).

## V. CONCLUSION

In this paper the short channel effects in MOSFET devices are discussed. The goal of the paper is to present a set of simulation experiments, in order a detailed examination of these effects to be performed.

## REFERENCES

- [1] Dr. Lynn Fuller, *The Short Channel MOSFET*, Microelectronic Engineering Rochester Institute of Technology, <a href="https://people.rit.edu/lffeee/mosfet\_s.pdf">https://people.rit.edu/lffeee/mosfet\_s.pdf</a>

- [2] Milaim Zabeli, Nebi Caka, Myzafere Limani, Qamil Kabashi, The impact of MOSFET's physical parameters on its threshold voltage, Proceedings of the 6th WSEAS International onference on Microelectronics, Nanoelectronics, Optoelectronics, Istanbul, Turkey, May 27-29, 2007

- [3] Thomas H. Lee Handout #2: EE214 Fall 2002A Review of MOS Device Physics; <a href="https://web.stanford.edu/class/archive/ee/ee214/ee214.1032/Handouts/HO2.pdf">https://web.stanford.edu/class/archive/ee/ee214/ee214.1032/Handouts/HO2.pdf</a>

- [4] Twesha Patel, *Comparison of Level 1, 2 and 3 MOSFET's* Course: Advanced Electronics, Semester: Fall 2014

- [5] Prof. Wu, Lecture 17 EE105Spring 2008, UC Berkeley, http://inst.eecs.berkeley.edu/~ee105/p10/lectures/lecture17.pdf

- [6] Prof.J.S.Smith,MOS Transistor models:Body effects, SPICE models, Lecture15, EECS105 Spring 2004; https://inst.eecs. berkeley.edu/~ee105/sp04/handouts/lectures/Lecture15.pdf

- [7] SPICE MODEL PARAMETERS OF MOSFETS, https:// www.seas .upenn.edu / ~jan/spice/spice.MOSparamlist.html