# Design and Realization of a Synchronous Buck Converter with eGaN FETs

Zoran B. Zivanovic<sup>1</sup> and Vladimir J. Smiljakovic<sup>2</sup>

*Abstract* – This paper presents the straightforward design of a synchronous buck converter using the Gallium Nitride transistors. The operating principles are briefly explained, including the functional block diagram. The prototype has been built and tested through lab measurements to verify the design. The goal was to demonstrate the capabilities of GaN transistors in order to show their significant advantages over silicon MOSFETs.

*Keywords* – Buck, efficiency, eGaN, Figure of Merit, synchronous.

# I. INTRODUCTION

Rapid commercialization of switch mode power supplies was made possible by mass production of silicon power MOSFETs in the late seventies. Constant demand for more efficient power converters, with higher efficiency and smaller size, forced the power supply engineers to reduce losses and increase the switching frequency. After 30 years, silicon MOSFET development has approached its theoretical limits. In contrast, the production of the enhancement mode gallium nitride FETs started in 2009, and is less investigated in literature [1]-[5]. A major factor in eGaN FETs performance is die (Fig. 1) that minimizes parasitic elements and allows footprint that helps to make optimal layout design. Interleaved drain and source bars generate small loops with opposing current flow, resulting into magnetic field cancellation and smaller common source inductance.

Fig. 1. eGaN EPC2015C passivated die (size 4.6 x 1.6 mm)

The objective of this paper is to contribute to the analysis of eGaN FETs characteristics by measuring the efficiency and capturing the waveforms of the synchronous buck converter with eGaN FETs over a wide range of operating conditions.

The paper is organized as follows. In Section II, synchronous buck converter basics are given. Two state of the art MOSFETs are compared with two eGaN FETS with the same voltage rating in section III with calculations of critical

<sup>1</sup>Zoran Zivanovic is with the IMTEL KOMUNIKACIJE AD, Bul. Mihajla Pupina 165b, 11070 Belgrade, Serbia, E-mail: zoki@insimtel.com.

<sup>2</sup>Vladimir Smiljakovic is with the IMTEL KOMUNIKACIJE AD, Bul. Mihajla Pupina 165b, 11070 Belgrade, Serbia, E-mail: smiljac@insimtel.com. parameters and components using design equations. Experimental results of a synchronous buck converter with eGaN FETs are presented in section IV to validate design. At the end, the conclusions are given in section V.

### II. SYNCHRONOUS BUCK CONVERTER BASICS

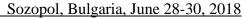

The synchronous buck converter is given in Fig. 2.

Fig. 2. Synchronous buck converter

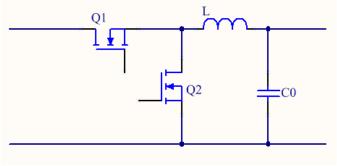

When the switch  $Q_1$  is ON during  $T_{ON}$  the energy is transferred to the output as well as to the inductor L. The current flows through the switch  $Q_1$  and the inductor. The difference of voltages between  $V_{IN}$  and  $V_{OUT}$  is applied to the inductor and the inductor and switch current  $I_{D1}$  rises linearly. During the OFF period of time, when the switch  $Q_1$  is OFF, the inductor current continues to supply load current. The switch  $Q_2$  is ON providing freewheeling path for the inductor current. The output voltage is applied to the inductor, so the inductor current decreases linearly (Fig. 3).

Fig. 3. Synchronous buck converter waveforms

The inductor current flows to the capacitor and the load. The capacitor  $C_0$  acts as a reservoir and holds the output voltage nearly constant.

### **III. DESIGN AND ANALYSIS**

To design synchronous buck converter we will start from the design specifications given in Table I.

TABLE I DESIGN SPECIFICATIONS

|                      |                  | Min  | Тур | Max |     |

|----------------------|------------------|------|-----|-----|-----|

| Input voltage        | V <sub>IN</sub>  | 8    | 12  | 18  | V   |

| Output voltage       | Vo               | 5    |     |     | V   |

| Output current       | Io               | 0.1  | 7   |     | А   |

| Output current limit | I <sub>OCL</sub> | 8.4  |     |     | А   |

| Full load efficiency | η                | > 90 |     |     | %   |

| Switching frequency  | $f_{SW}$         | 440  |     |     | KHz |

In order to dampen sub-harmonic oscillation, the minimum inductor value should be calculated as

$$L = \frac{V_o}{0.3f_{sw}I_o} \tag{1}$$

The maximum and minimum duty cycle can be calculated as

$$D_{MAX} = \frac{V_O}{V_{INMIN}} \tag{2}$$

$$D_{MIN} = \frac{V_O}{V_{INMAX}} \tag{3}$$

The peak to peak inductor current is

$$\Delta I = \frac{V_{INM} - V_O}{L} \frac{D_{MIN}}{f_{SW}} \tag{4}$$

Knowing that the peak inductor current is

$$I_{pk} = I_O + \frac{\Delta I}{2} \tag{5}$$

The output capacitor must be large enough to limit the voltage overshoots and undershoots during the load change transients. The minimum value of output capacitor is

$$C_{O\min} = \frac{LI_{step}^2}{2\Delta V_O D_{MAX} (V_{INM} - V_O)}$$

(6)

The power switches must be chosen with voltage rating to

withstand the maximum input voltage and also they must be capable of delivering the load current. Knowing that, our choice is two MOSFETs (IPC50N04S5L-5R5 and IPZ40N04S5L-7R4) and two eGaNs (EPC2014C and EPC2015C). We will use figure of merit (FOM) expressed by the equation

$$FOM = (Q_{GD} + Q_{GS})R_{DS}$$

(7)

as a selection criteria. Results are given in Table II. Although both MOSFETs are state of the art power switches, the eGaN FETs are better choice because of superior switching characteristics and zero reverse recovery time.

TABLE II

Power switch characteristics

|             | $Q_{GD}$ | Q <sub>GS</sub> | R <sub>DS</sub> | FOM   | Qrr  |

|-------------|----------|-----------------|-----------------|-------|------|

| IPC50N04S5L | 3.6nC    | 2.7nC           | 5.7mΩ           | 35.91 | 22ns |

| IPZ40N04S5L | 3.0nC    | 2.0nC           | 7.9mΩ           | 39.5  | 26ns |

| EPC2014C    | 0.3nC    | 0.7nC           | 12mΩ            | 12    | Ons  |

| EPC2015C    | 1.2nC    | 2.7nC           | 3.2mΩ           | 12.48 | Ons  |

The high side FET losses can be calculated as

$$P_{DQ1} = I_O^2 R_{DS} D_{MAX} + \frac{1}{2} V_{IN} (t_r + t_f) I_O f_{SW}$$

(8)

The losses in the low side FET can be expressed as

$$P_{DQ2} = I_{O}^{2} R_{DS} (1 - D_{MIN}) + I_{O} (t_{dr} + t_{df}) f_{SW} V_{D}$$

$$+ Q_{rr} f_{SW} V_{IN}$$

(9)

Calculated values are given in Table III.

TABLE III CALCULATED VALUES

| Inductance calculated | L          | 5.4   | μH |

|-----------------------|------------|-------|----|

| Inductance adopted    | L          | 6.8   | μH |

| Max duty cycle        | $D_{MAX}$  | 0.625 |    |

| Min duty cycle        | $D_{MIN}$  | 0.277 |    |

| Peak to peak current  | $\Delta I$ | 1.2   | А  |

| Peak current          | $I_{pk}$   | 7.6   | А  |

| Min capacitance       | $C_{Omin}$ | 290   | μF |

We will also adjust passive components around the error amplifier in order to have 25 kHz loop bandwidth with  $60^{\circ}$  phase margin.

### IV. REALIZATION

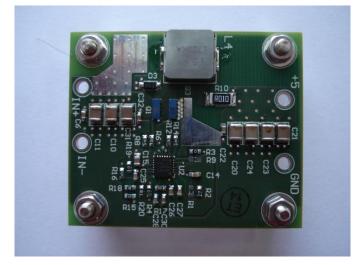

The synchronous buck converter has been realized on a four layer FR-4 substrate, with a thickness of 1.6mm and 50 $\mu$ m copper on outer layers and 35  $\mu$ m on inner layers. The size of

the PCB is 50x42 mm. For the high-side and low-side switches we have used eGaN FETs EPC2015C. The eGaN FETs have a maximum gate voltage of +6V. The buck controller LM5141, require a logic-level FETs, so it is a great choice for this design. The output filter is made of four pcs of multilayer ceramic capacitors  $47\mu$ F, 10V, X7R, to reduce high frequency noise and two 100  $\mu$ F, 10V tantalum capacitors for energy storage.

Using lab power supply and electronic load, we have recorded the waveforms of interest and measured efficiency at various loads and input voltages.

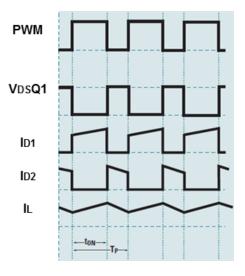

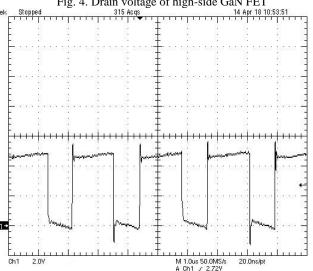

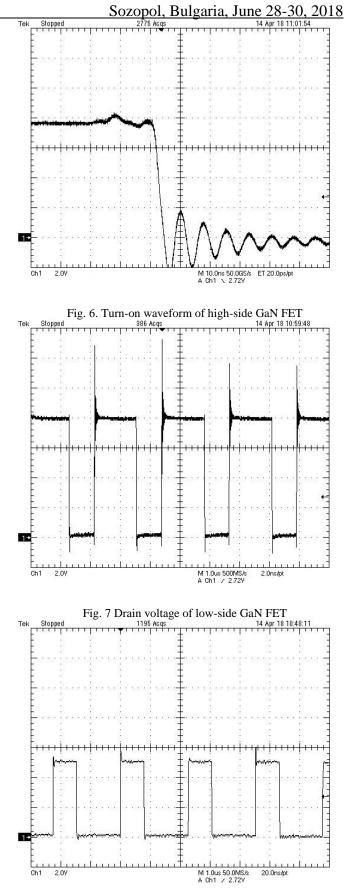

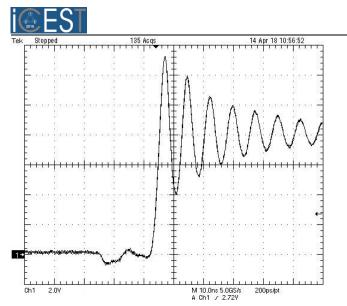

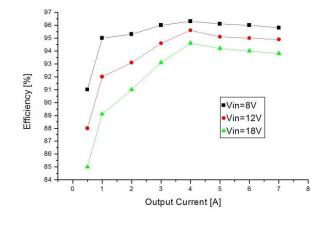

Drain voltage of the high side GaN FET is given in Fig. 4. His gate voltage is given in Fig. 5. Turn-on waveform of highside GaN FET with parasitic 125 MHz ringing is given in Fig. 6. Drain voltage of the low-side side GaN FET is given in Fig. 7 and his gate voltage is given in Fig. 8. The 125 MHz ringing on the drain of the low-side GaN FET at turn-off is given in Fig. 9. Measured efficiency of the converter is given in Fig. 10.

Fig. 5. Gate voltage of high-side GaN FET

Fig. 8. Gate voltage of low-side GaN FET

Fig. 9. The ringing on the drain of low-side GaN FET at turn-off

Sozopol, Bulgaria, June 28-30, 2018

## V. CONCLUSION

In this paper the design and realization of a synchronous buck converter with GaN FETs is presented. Calculations and experimental results are presented. The prototype was built and tested. The results verified that the efficiency can go as high as 96%.

### ACKNOWLEDGEMENT

The work is partially supported by the Serbian Ministry of Education and Science (Project III-45016). The authors would like to thank Texas Instruments for providing buck controller samples.

#### REFERENCES

- Zoran Zivanovic, Vladimir Smiljakovic, "Design and Realization of a eGaN FET DCDC Converter", TELFOR2014 Proceedings, pp. 637-640

- [2] Zoran Zivanovic, Vladimir Smiljakovic, Sinisa Jovanovic "Analysis and Design of a Resonant Reset GaN Forward Converter with Self-Driven Synchronous Rectifiers", ICEST2015 Proceedings, pp. 275-278

- [3] Zoran Zivanovic, Vladimir Smiljakovic, "Design and Realization of a Interleaved Boost Converter with GaN FETs and SiC Diodes", ICETRAN2017, pp. ELI2.3.1-4

- [4] Zhi-Wei Xu, Zhi-Liang Zhang, Ke Xu, Zhou Dong and Xiaoyong Ren, "2-MHz GaN PWM Isolated SEPIC Converters", 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 149-156

- [5] Johan Delaine, Pierre-Olivier Jeannin, David Frey, Kevin Guepratte, "High Frequency DC-DC Converter Using GaN Device", 2012 Twenty-Seventh Annual IEEE Applied Power Electronics Conference and Exposition (APEC), pp. 1757-1761

Fig. 10. Measured efficiency vs. output current

Fig. 11. The converter prototype